EDSFF(E1.S/E1.L) PCIe 5.0 Test Fixtures

Key features:

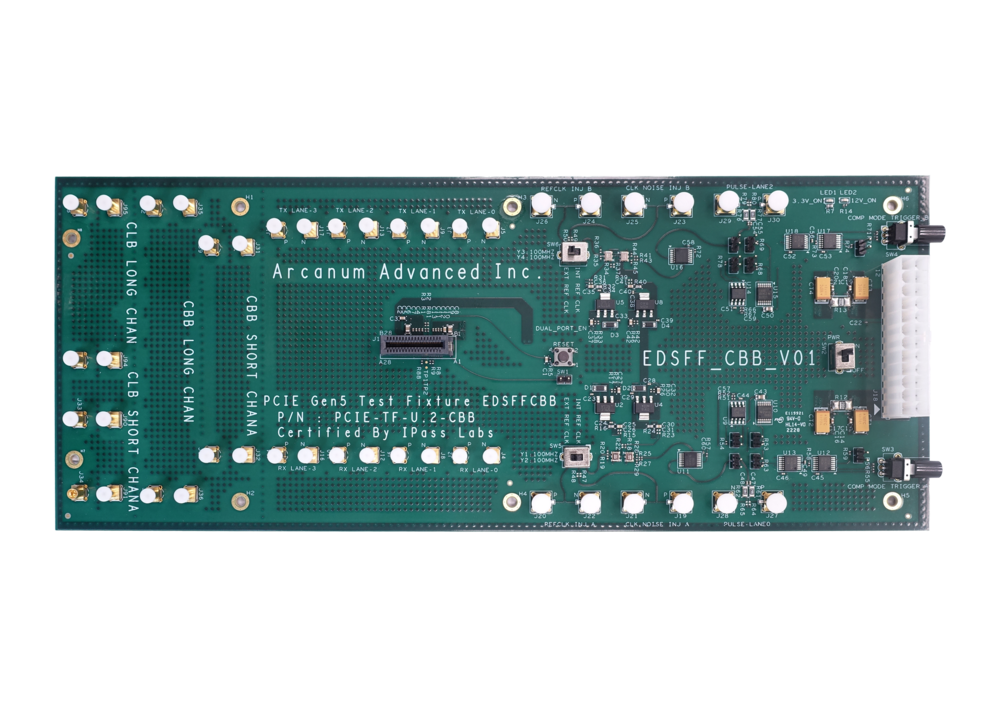

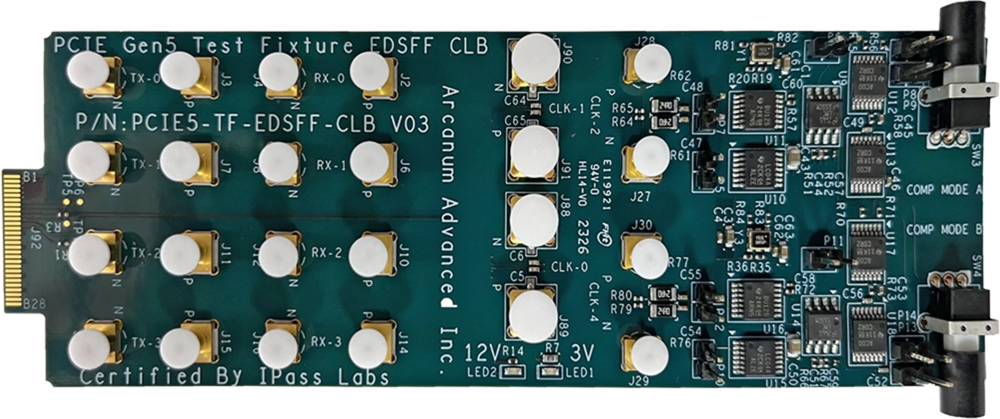

There are three separated boards: two CLBs and one CBB.

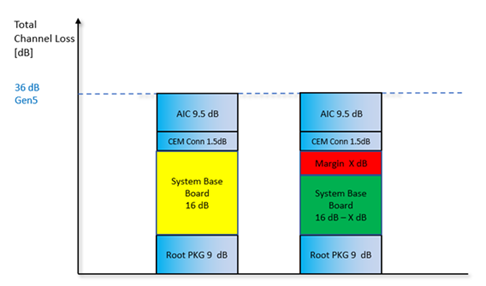

- Signal Integrity Board for EDSFF(SFF-TA-1006, SFF-TA-1007) Physical Layer Conformance.

- CLB supports PCIe5.0 (32GT/s) used for testing Transmitters.

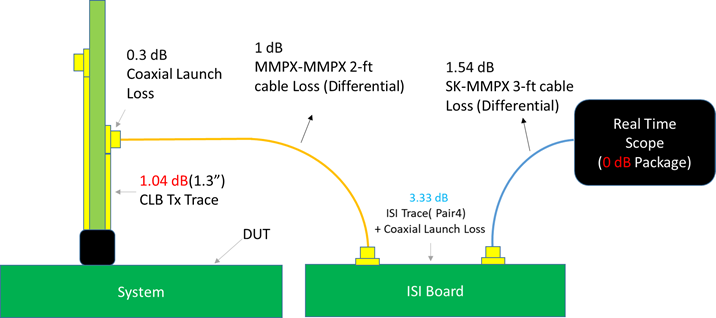

- CLB needs additional Gen5 CEM (SIG-REV4) ISI Board for the testing.

- CBB supports PCIe5.0 (32GT/s) used for testing Receivers.

- MMPX connectoris 100% compatiblewith PCI-SIG CEM ISI board.

- Real testing result of loss budget is 7.21 dB